【加法笔记系列】逻辑门、半加器、全加器、波纹进位加法器

本文共 651 字,大约阅读时间需要 2 分钟。

在之前了解 PN 结以及逻辑电路实现之后,终于可以开始尝试实现计算机的加法了。

- 逻辑门,包括与、或、与非、异或

- 半加器,半加器电路

- 全加器,全加器电路

- 波纹进位加法器

逻辑门

与门 AND

或门 OR

与非门 NAND

异或门 XOR

真值表

| A | B | AND | OR | NAND | XOR |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 |

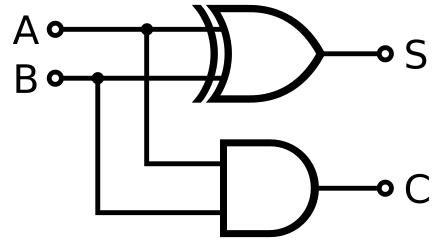

半加器

半加器(half adder)的功能是将两个一位二进制数相加。它具有两个输入和两个输出(分别是和(sum)、进位(carry))。

— Wiki

半加器电路图

| A | B | Carry | Sum |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

半加器简化图

全加器

全加器(full adder)将两个一位二进制数相加,并根据接收到的低位进位信号,输出和、进位输出。全加器的三个输入信号为两个加数A、B和低位进位Cin。

全加器逻辑电路

该电路如用简化版半加器表示,可以如下图:

全加器真值表

二进制的全加器,刚可以用两位表示最大值,即 1 + 1 + 1 = 3 = 11(2)

| A | B | Cin | Cout | S |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

全加器简化图

或

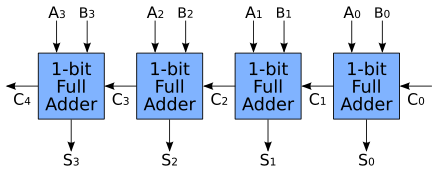

波纹进位加法器

如果不需要连接其他进位信号,则最低位的全加器可以用半加器替换。

References

更多文章访问:

转载地址:http://gglfm.baihongyu.com/

你可能感兴趣的文章

Web前端研发工程师编程能力飞升之路

查看>>

C#编程总结(十)字符转码

查看>>

linux gcc头文件搜索路径

查看>>

对线程的理解

查看>>

更改linux swappiness 提高物理内存使用率

查看>>

J-Link GDB Server Command

查看>>

如何用.NET生成二维码?

查看>>

C++一个简单的手柄类模板

查看>>

The Water Problem(排序)

查看>>

atitit.无线上网卡 无法搜索WiFi 解决无线路由器信号不能被连接

查看>>

C#进阶系列——DDD领域驱动设计初探(三):仓储Repository(下)

查看>>

android 电容屏(三):驱动调试之驱动程序分析篇

查看>>

数字签名时间戳服务器的原理 !

查看>>

C++ Split string into vector<string> by space

查看>>

JavaScript学习——内置属性

查看>>

Oracle Profile 使用详解--zhuanzai

查看>>

Hadoop-1.1.2、HBase-0.94.7完全分布式集群结构

查看>>

TP-Link wr703N 使用华为HiLink系列上网卡的设置【转】

查看>>

士兵杀敌(四)(树状数组+线段树)

查看>>

Linux 高可用(HA)集群基本概念2

查看>>